6

14

## Second Semester FYUGP Physics Examination APRIL 2025 (2024 Admission onwards) KU2DSCPHY125 (DIGITAL ELECTRONICS)

(DATE OF EXAM: 30-4-2025)

| Time | e: 90 min Maximum Mark                                                                                                                                                                       | s: 50    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| P    | Part A (Answer any 6 questions. Each carries 2 marks)                                                                                                                                        |          |

| 1.   | In the octal number system, write the four numbers that come after 7?                                                                                                                        | 2        |

| 2.   | What is Binary Coded Decimal (BCD)                                                                                                                                                           | 2        |

| 3.   | What is the weight of each 1 in BCD number 1000?                                                                                                                                             | 2        |

| 4.   | Determine the total number of possible input combinations for a 4-input gate.                                                                                                                | AND<br>2 |

| 5.   | A device is needed to indicate when two LOW levels occur simultaneously inputs and to produce a HIGH output as an indication. Specify the device.                                            | on its   |

| 6.   | State DeMorgan's second theorem?                                                                                                                                                             | 2        |

| 7.   | Express $\Lambda$ + B using three NAND gates.                                                                                                                                                | 2        |

| 8.   | What you mean by a full adder                                                                                                                                                                | 2        |

|      | Part B (Answer any 4 questions. Each carries 6 marks)                                                                                                                                        |          |

| 9.   | Convert each decimal number to octal by repeated division by 8:                                                                                                                              |          |

|      | (a) 359<br>(b) 439                                                                                                                                                                           | - 6      |

| 10.  | Explain the difference between positive and negative logic                                                                                                                                   | 6        |

| 11.  | How does an exclusive - OR gate differ from an OR gate in its logical oper                                                                                                                   | ation?   |

| 12.  | The Boolean expression for an exclusive-OR gate is AB+AB. With this as a stronger, use DeMorgan's theorems and any other rules or laws that are applications.                                |          |

|      | develop an expression for the exclusive-NOR gate.                                                                                                                                            | 6        |

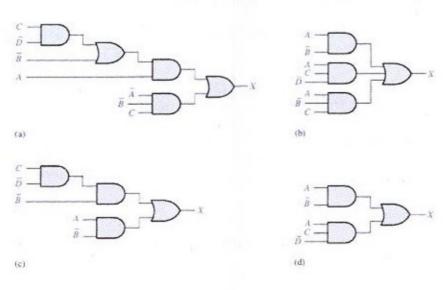

| 13.  | Implement $X=AB+CD$ using NAND gates.                                                                                                                                                        | 6        |

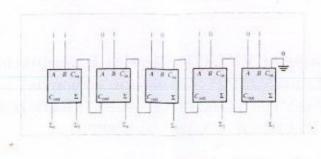

| 14.  | For the parallel adder in figure determine the complete sum by the analysis logical operations of the circuit. Verify the result by the direct addition of the circuit work and the circuit. | of the   |

|      | input numbers                                                                                                                                                                                |          |

Part C (Answer any 1 question(s). Each carries 14 marks)

- (a) Given an 8-bit binary number 10111010<sub>2</sub>, find its 1's complement and 2's complement, then determine its decimal equivalent.

(b) Compare Signed Magnitude 1's Complement and 2's Complement representations.

- (b) Compare Signed Magnitude, 1's Complement, and 2's Complement representations of negative numbers. Give an example of each and explain their advantages and disadvantages.

- 16. Determine which of the logic circuits in figure are equivalent